Очень крупномасштабная интеграция

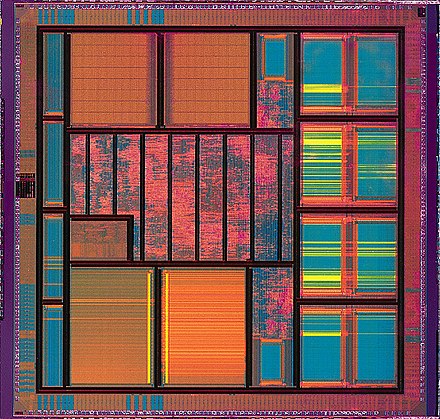

Сверхбольшая интеграция ( СБИС ) — это процесс создания интегральной схемы (ИС) путем объединения миллионов или миллиардов МОП -транзисторов на одном кристалле. СБИС началась в 1970-х годах, когда были разработаны и широко распространены микросхемы МОП-интегральных схем (МОП-схемы), что позволило реализовать сложные полупроводниковые и телекоммуникационные технологии. Микропроцессор и микросхемы памяти являются устройствами СБИС.

До внедрения технологии VLSI большинство ИС имели ограниченный набор функций, которые они могли выполнять. Электронная схема могла состоять из ЦП , ПЗУ , ОЗУ и другой связующей логики . VLSI позволяет разработчикам ИС добавлять все это в один чип .

История

Фон

История транзистора восходит к 1920-м годам, когда несколько изобретателей пытались создать устройства, предназначенные для управления током в твердотельных диодах и преобразования их в триоды. Успех пришел после Второй мировой войны, когда использование кристаллов кремния и германия в качестве детекторов радаров привело к улучшениям в производстве и теории. Ученые, работавшие над радаром, вернулись к разработке твердотельных устройств. С изобретением первого транзистора в Bell Labs в 1947 году область электроники перешла от вакуумных ламп к твердотельным устройствам . [1]

Имея в руках небольшой транзистор, инженеры-электрики 1950-х годов увидели возможности создания гораздо более сложных схем. Однако по мере роста сложности схем возникали проблемы. [2] Одной из проблем был размер схемы. Сложная схема, такая как компьютер, зависела от скорости. Если компоненты были большими, провода, соединяющие их, должны были быть длинными. Электрическим сигналам требовалось время, чтобы пройти через схему, что замедляло работу компьютера. [2]

Изобретение интегральной схемы Джеком Килби и Робертом Нойсом решило эту проблему, сделав все компоненты и чип из одного блока (монолита) полупроводникового материала. [3] Схемы можно было сделать меньше, а процесс производства можно было автоматизировать. Это привело к идее интеграции всех компонентов на монокристаллической кремниевой пластине, что привело к малой интеграции (SSI) в начале 1960-х годов, а затем к средней интеграции (MSI) в конце 1960-х годов. [4]

СБИС

General Microelectronics представила первую коммерческую МОП- интегральную схему в 1964 году. [5] В начале 1970-х годов технология МОП-интегральных схем позволила интегрировать более 10 000 транзисторов в одну микросхему. [6] Это проложило путь для СБИС в 1970-х и 1980-х годах с десятками тысяч МОП-транзисторов на одной микросхеме (позже сотни тысяч, затем миллионы, а теперь миллиарды).

Первые полупроводниковые чипы содержали по два транзистора каждый. Последующие достижения добавили больше транзисторов, и, как следствие, со временем было интегрировано больше отдельных функций или систем. Первые интегральные схемы содержали всего несколько устройств, возможно, до десяти диодов , транзисторов , резисторов и конденсаторов , что позволяло изготавливать один или несколько логических вентилей на одном устройстве. Теперь ретроспективно известные как маломасштабная интеграция (SSI), усовершенствования в технике привели к устройствам с сотнями логических вентилей, известным как среднемасштабная интеграция (MSI). Дальнейшие усовершенствования привели к крупномасштабной интеграции (LSI), то есть системам с как минимум тысячей логических вентилей. Современная технология далеко продвинулась дальше этой отметки, и сегодняшние микропроцессоры имеют много миллионов вентилей и миллиардов отдельных транзисторов.

В свое время была предпринята попытка назвать и откалибровать различные уровни интеграции большого масштаба выше VLSI. Использовались такие термины, как сверхбольшая интеграция (ULSI). Но огромное количество вентилей и транзисторов, доступных на обычных устройствах, сделало такие тонкие различия спорными. Термины, предполагающие уровни интеграции выше VLSI, больше не используются широко.

В 2008 году процессоры с миллиардом транзисторов стали коммерчески доступными. Это стало более распространенным явлением по мере того, как производство полупроводников развивалось с текущего поколения процессоров 65 нм . Текущие разработки, в отличие от самых ранних устройств, используют обширную автоматизацию проектирования и автоматизированный логический синтез для компоновки транзисторов, что обеспечивает более высокий уровень сложности в результирующей логической функциональности. Некоторые высокопроизводительные логические блоки, такие как ячейка SRAM ( статическая память с произвольным доступом ), по-прежнему разрабатываются вручную для обеспечения наивысшей эффективности. [ необходима цитата ]

Структурированный дизайн

Структурированное проектирование СБИС — это модульная методология, созданная Карвером Мидом и Линн Конвэй для экономии площади микросхемы путем минимизации площади соединительной ткани. Это достигается путем повторяющегося расположения прямоугольных макроблоков, которые могут быть соединены между собой с помощью проводки с помощью упора. Примером может служить разбиение макета сумматора на ряд ячеек с равными битовыми срезами. В сложных конструкциях такое структурирование может быть достигнуто путем иерархического вложения. [7]

Структурированное проектирование СБИС было популярно в начале 1980-х годов, но позже потеряло свою популярность [ требуется ссылка ] из-за появления инструментов размещения и маршрутизации, тратящих много места на маршрутизацию , что допускается благодаря прогрессу закона Мура . При представлении языка описания оборудования KARL в середине 1970-х годов Райнер Хартенштейн ввел термин «структурированное проектирование СБИС» (первоначально как «структурированное проектирование БИС»), повторяя подход Эдсгера Дейкстры к структурному программированию путем вложения процедур, чтобы избежать хаотичных спагетти-структурированных программ.

Трудности

Поскольку микропроцессоры становятся все более сложными из-за масштабирования технологий , проектировщики микропроцессоров сталкиваются с рядом проблем, которые заставляют их выходить за рамки проектирования и смотреть вперед в посткремниевую эпоху:

- Изменение процесса – Поскольку методы фотолитографии приближаются к фундаментальным законам оптики, достижение высокой точности в концентрациях легирования и протравленных проводах становится все более сложным и подверженным ошибкам из-за изменения. Теперь проектировщики должны проводить моделирование на нескольких углах процесса изготовления , прежде чем чип будет сертифицирован как готовый к производству, или использовать методы системного уровня для работы с эффектами изменения. [8] [9]

- Более строгие правила проектирования – Из-за проблем с литографией и травлением при масштабировании проверка правил проектирования для макета становится все более строгой. Проектировщики должны помнить о постоянно растущем списке правил при компоновке пользовательских схем. Накладные расходы на индивидуальный дизайн сейчас достигают критической точки, и многие дизайнерские дома решают перейти на инструменты автоматизации электронного проектирования (EDA) для автоматизации своего процесса проектирования. [10]

- Закрытие тайминга/проекта – Поскольку тактовые частоты имеют тенденцию к увеличению, проектировщикам становится все труднее распределять и поддерживать низкий перекос тактовых частот между этими высокочастотными тактовыми частотами по всему чипу. Это привело к росту интереса к многоядерным и многопроцессорным архитектурам, поскольку общее ускорение может быть получено даже при более низкой тактовой частоте за счет использования вычислительной мощности всех ядер. [11]

- Успех первого прохода – По мере уменьшения размеров кристаллов (из-за масштабирования) и увеличения размеров пластин (из-за снижения производственных затрат) количество кристаллов на пластину увеличивается, и сложность изготовления подходящих фотошаблонов быстро возрастает. Набор масок для современной технологии может стоить несколько миллионов долларов. Эти единовременные расходы сдерживают старую итеративную философию, включающую несколько «циклов вращения» для поиска ошибок в кремнии, и поощряют успех кремния первого прохода. Было разработано несколько философий проектирования, чтобы помочь этому новому потоку проектирования, включая проектирование для производства ( DFM ), проектирование для тестирования ( DFT ) и проектирование для X. [12 ]

- Электромиграция

Смотрите также

- Специализированная интегральная схема

- Космический куб Калтеха

- Модель логики интерфейса

- Список заводов по производству полупроводников

- Революция в проектировании микросхем VLSI Мида–Конвея

- Нейроморфная инженерия

- Поликристаллический кремний

- Система на кристалле (SoC)

Ссылки

- ^ Зорпетт, Гленн (20 ноября 2022 г.). «Как работал первый транзистор». IEEE Spectrum .

- ^ ab "История интегральной схемы". Nobelprize.org. Архивировано из оригинала 29 июня 2018 года . Получено 21 апреля 2012 года .

- ^ "BBC - История - Исторические личности: Килби и Нойс (1923-2005)". www.bbc.co.uk . Получено 10 августа 2024 г. .

- ^ О'Реган, Джерард (2016), О'Реган, Джерард (ред.), «Изобретение интегральной схемы и рождение Кремниевой долины», Введение в историю вычислений: учебник по истории вычислений , Темы бакалавриата по информатике, Cham: Springer International Publishing, стр. 93–100, doi : 10.1007/978-3-319-33138-6_7, ISBN 978-3-319-33138-6, получено 10 августа 2024 г.

- ^ "1964: Представлена первая коммерческая МОП-ИС". Музей истории компьютеров .

- ^ Хиттингер, Уильям С. (1973). «Технология металл-оксид-полупроводник». Scientific American . 229 (2): 48–59. Bibcode : 1973SciAm.229b..48H. doi : 10.1038/scientificamerican0873-48. ISSN 0036-8733. JSTOR 24923169.

- ^ Джейн, БК (август 2009). Цифровая электроника - современный подход БК Джейна. Издательство Global Vision. ISBN 9788182202153. Получено 2 мая 2017 г.

- ^ У, Цян; Ли, Яньли; Ян, Юйшу; Чэнь, Шоумян; Чжао, Юйхан (26 июня 2020 г.). «Закон, направляющий развитие технологии фотолитографии, и методология проектирования фотолитографического процесса». Международная конференция по полупроводниковым технологиям Китая 2020 г. (CSTIC) . IEEE. стр. 1–6. doi : 10.1109/CSTIC49141.2020.9282436. ISBN 978-1-7281-6558-5.

- ^ «Изучение проблем проектирования СБИС: преодоление сложности для достижения успеха». InSemi Tech . Получено 10 августа 2024 г.

- ^ Ван, Лаунг-Тернг; Чанг, Яо-Вэнь; Ченг, Кван-Тин (Тим) (февраль 2009 г.). Автоматизация электронного проектирования: синтез, проверка и тестирование. Сан-Франциско, Калифорния, США: ISBN Morgan Kaufmann Publishers Inc. 978-0-08-092200-3.

- ^ "Clock Skew in STA". 23 июня 2024 г. Получено 10 августа 2024 г.

- ^ Ригер, Майкл Л. (26 ноября 2019 г.). «Ретроспектива масштабирования значений СБИС и литографии». Журнал микро/нанолитографии, МЭМС и МОЭМС . 18 (4): 040902. Bibcode : 2019JMM&M..18d0902R. doi : 10.1117/1.JMM.18.4.040902. ISSN 1932-5150.

Дальнейшее чтение

- Бейкер, Р. Якоб (2010). КМОП: проектирование схем, компоновка и моделирование, третье издание . Wiley-IEEE. стр. 1174. ISBN 978-0-470-88132-3.

- Весте, Нил Х. Э. и Харрис, Дэвид М. (2010). Проектирование КМОП СБИС: перспективы схем и систем, четвертое издание . Бостон: Pearson/Addison-Wesley. стр. 840. ISBN 978-0-321-54774-3.

- Чен, Вай-Кай (2007). Справочник по СБИС . Бока-Ратон, Флорида: CRC/Taylor & Francis. ISBN 978-1-4200-0596-7. OCLC 83977431.

- Мид, Карвер А .; Конвей, Линн (1980). Введение в системы СБИС . Бостон: Addison-Wesley. ISBN 0-201-04358-0.

Внешние ссылки

- Лекции по проектированию и внедрению систем СБИС в Университете Брауна

- Проектирование систем СБИС