Программируемая логическая матрица

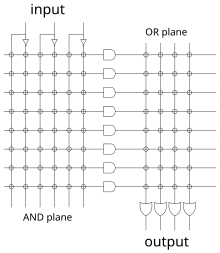

Программируемая логическая матрица ( PLA ) — это разновидность программируемого логического устройства , используемого для реализации комбинационных логических схем . PLA имеет набор программируемых плоскостей вентилей И , которые связаны с набором программируемых плоскостей вентилей ИЛИ , которые затем могут быть условно дополнены для получения выхода. Он имеет 2 N вентилей И для N входных переменных, а для M выходов из PLA должно быть M вентилей ИЛИ, каждый с программируемыми входами от всех вентилей И. Такая компоновка позволяет синтезировать множество логических функций в канонических формах суммы произведений .

PLA отличаются от программируемых логических устройств на основе матриц ( PAL и GAL ) тем, что плоскости вентилей И и ИЛИ являются программируемыми. PAL имеет программируемые вентили И, но фиксированные вентили ИЛИ [ требуется разъяснение ]

История

В 1970 году Texas Instruments разработала программируемую по маске ИС на основе ассоциативной памяти IBM только для чтения или ROAM. Это устройство, TMS2000, программировалось путем изменения металлического слоя во время производства ИС. TMS2000 имел до 17 входов и 18 выходов с 8 JK-триггерами для памяти. TI ввела термин Programmable Logic Array для этого устройства. [1]

Процедура внедрения

- Подготовка в форме СОП ( сумма продуктов ).

- Получите минимальную форму СОП, чтобы свести количество терминов, касающихся продукта, к минимуму.

- Определите входное соединение матрицы И для генерации требуемого термина продукта.

- Затем определите входные соединения матрицы ИЛИ для генерации членов суммы.

- Определите связи матрицы инверсии.

- Запрограммируйте PLA.

Блок-схема PLA:

| 1-Й БЛОК | 2-Й БЛОК | 3-Й БЛОК | 4-Й БЛОК | 5-Й БЛОК |

|---|---|---|---|---|

| ВХОДНОЙ БУФЕР | И МАТРИЦА | ИЛИ МАТРИЦА | ИНВЕРТИРОВАННАЯ/НЕИНВЕРТИРОВАННАЯ МАТРИЦА | ВЫХОДНОЙ БУФЕР ТРИГАНТА |

Преимущества перед памятью, доступной только для чтения

Желаемые выходы для каждой комбинации входов могут быть запрограммированы в постоянное запоминающее устройство , при этом входы будут управляться адресной шиной, а выходы будут считываться как данные. Однако это потребовало бы отдельной области памяти для каждой возможной комбинации входов, включая комбинации, которые никогда не должны возникать, а также дублирования данных для условий «неважно» (например, логика типа «если вход A равен 1, то, что касается выхода X, нам все равно, что такое вход B»: в ПЗУ это должно было бы быть записано дважды, один раз для каждого возможного значения B, и по мере добавления большего количества «неважно» входов дублирование растет экспоненциально); поэтому программируемая логическая матрица часто может реализовать часть логики, используя меньше транзисторов, чем эквивалент в постоянном запоминающем устройстве. Это особенно ценно, когда она является частью процессорной микросхемы, где транзисторов мало (например, исходная микросхема 6502 содержала PLA для управления различными операциями процессора [2] ).

Приложения

Одно из применений PLA — реализация управления через тракт данных . Он определяет различные состояния в наборе инструкций и создает следующее состояние (путем условного ветвления). [например, если машина находится в состоянии 2 и перейдет в состояние 4, если инструкция содержит непосредственное поле; тогда PLA должна определить действия элемента управления в состоянии 2, установить следующее состояние на 4, если инструкция содержит непосредственное поле, и определить действия элемента управления в состоянии 4]. Программируемые логические массивы должны соответствовать диаграмме состояний для системы.

Самые первые домашние компьютеры Commodore 64 , выпущенные в 1982 году (в начале 1983 года), изначально использовали программируемый PLA Signetics 82S100, но по мере роста спроса MOS Technology / Commodore Semiconductor Group начали производить программируемый по маске PLA, который имел номер детали 906114-01. [3]

Смотрите также

Ссылки

- ^ Андрес, Кент (октябрь 1970 г.). Отчет о применении Texas Instruments: программируемые логические матрицы МОП . Texas Instruments. Бюллетень CA-158.

- ^ Как на самом деле работают нелегальные коды операций MOS 6502

- ^ arcadecomponents.com - Commodore 906114-01 64 PLA IC

Внешние ссылки

- «Программируемая логическая матрица (PLA)». cmsc311 . Университет Мэриленда . 2003. Архивировано из оригинала 2017-12-14.

- "PLA (программируемая логическая матрица)". Java Applet . Университет Гамбурга . Архивировано из оригинала 2013-01-15 . Получено 2010-04-07 .