План этажа (микроэлектроника)

Изображения в этой статье могут потребовать корректировки размещения , форматирования и размера изображений . ( Май 2024 г. ) |

В области автоматизации проектирования электронных устройств план интегральной схемы представляет собой схематическое изображение предполагаемого размещения ее основных функциональных блоков.

В современном электронном проектировании планы этажей создаются на этапе проектирования планировки этажей , раннем этапе иерархического подхода к проектированию интегральных схем .

В зависимости от используемой методологии проектирования фактическое определение плана этажа может отличаться.

Планировка этажей

Планировка этажей учитывает некоторые геометрические ограничения в дизайне. Вот несколько примеров:

- Контактные площадки для внешних соединений (часто с использованием проволочной связи ) обычно располагаются по периферии чипа;

- Часто линейные драйверы приходится располагать как можно ближе к контактным площадкам;

- Поэтому в некоторых случаях площадь чипа определяется минимальной площадью, необходимой для размещения необходимого количества контактных площадок;

- области кластеризуются для ограничения путей передачи данных, поэтому часто содержат определенные структуры, такие как кэш -память , умножитель , устройство сдвига , драйвер линии и арифметико-логическое устройство ;

- Приобретенные блоки интеллектуальной собственности ( IP-блоки ), такие как ядро процессора , поставляются в предопределенных блоках областей;

- некоторые IP-блоки имеют правовые ограничения, например, запрещающие маршрутизацию сигналов непосредственно над блоком.

Математические модели и задачи оптимизации

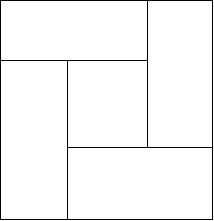

В некоторых подходах план этажа может быть разделом всей площади чипа на выровненные по осям прямоугольники , которые будут заняты блоками IC. Это разделение подчиняется различным ограничениям и требованиям оптимизации: площадь блока, соотношение сторон , предполагаемая общая мера межсоединений и т. д.

Поиск хороших планов этажей был областью исследований в комбинаторной оптимизации . Большинство задач, связанных с поиском оптимальных планов этажей, являются NP-трудными , т.е. требуют огромных вычислительных ресурсов. Поэтому наиболее распространенным подходом является использование различных эвристик оптимизации для поиска хороших решений.

Другой подход заключается в ограничении методологии проектирования определенными классами планов этажей, такими как многослойные планы этажей.

Планы этажей, которые можно разбить на части

План этажа, который можно разбить на слои, — это план этажа, который можно определить рекурсивно, как описано ниже. [1]

- План этажа, состоящий из одного прямоугольного блока, можно разрезать.

- Если блок из плана этажа, который можно разрезать, разрезать («нарезать») на две части вертикальной или горизонтальной линией, то полученный план этажа можно разрезать.

Нарезные планы этажей использовались в ряде ранних инструментов автоматизации электронного проектирования [1] по ряду причин. Нарезные планы этажей могут быть удобно представлены бинарными деревьями (точнее, k -d деревьями ), которые соответствуют порядку нарезки. Что еще более важно, ряд NP-трудных задач с планами этажей имеют полиномиальные алгоритмы времени, когда ограничиваются нарезными планами этажей. [2]

Дальнейшее чтение

- Планировщик чипов системы PLAYOUT

- Физическое проектирование СБИС: от разбиения графа до временного замыкания, Кан, Лиениг, Марков и Ху, doi : 10.1007/978-3-030-96415-3 ISBN 978-3-030-96414-6 , 2022

- Основы проектирования топологии электронных схем, Лиениг, Шайбле, Springer, doi : 10.1007/978-3-030-39284-0 ISBN 978-3-030-39284-0 , 2020

Ссылки

- ^ ab "Справочник по электротехнике", Ричард К. Дорф (1997) ISBN 0-8493-8574-1

- ^ Саррафзаде, М., «Преобразование произвольного плана этажа в разрезаемый», Труды Международной конференции IEEE/ACM по автоматизированному проектированию (ICCAD-93) 1993 г., стр. 386-389.